服务热线

0755-88364040

18902464556

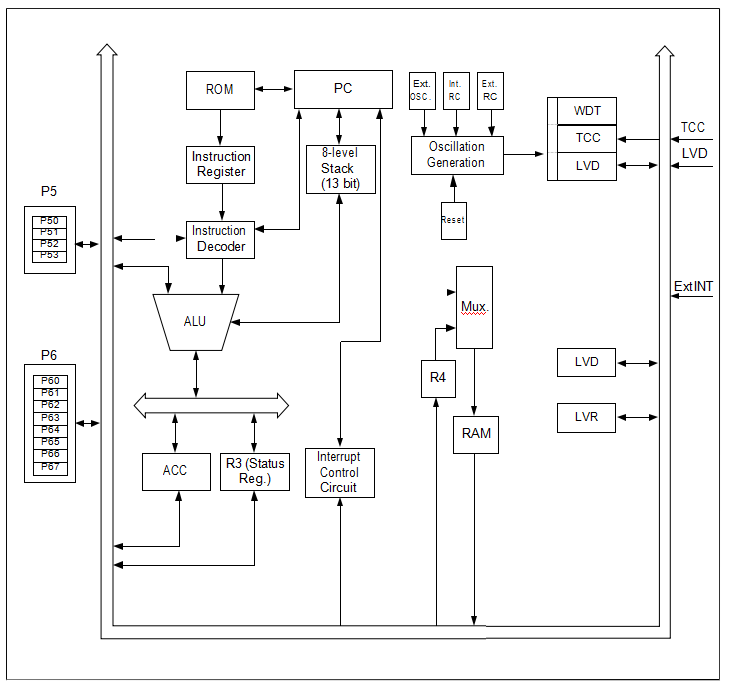

EM78P173N 是一款采用低功耗、高速 CMOS 技术设计和开发的 8 位微处理器。它具有片上 1K´13 位电气一次性可编程只读存储器 (OTP-ROM)。该设备提供了一个保护位,以防止入侵用户的 OTP 内存代码。还提供三个代码选项词,以满足用户的需求。

凭借其增强的 OTP-ROM 功能,EM78P173N 提供了一种开发和验证用户程序的便捷方式。此外,该 OTP 设备使用开发和编程工具提供简单有效的程序更新优势。用户可以利用 ELAN Writer 轻松编写他们的开发代码。

特点

CPU 配置

-1K´13 位片上 ROM

-48 8 位片上寄存器 (SRAM,通用)

-5 级堆栈用于子程序嵌套

-4 可编程电平电压检测器 LVD : 4.5, 4.0, 3.3, 2.2V

-3 可编程电平电压复位 LVR : 4.0, 3.5, 2.7V

-在 5V/4MHz 时小于 1.5mA

-通常为 15 μA,3V/32kHz

-通常为 1 µA,在睡眠模式期间

I/O 端口配置

-2 个双向 I/O 端口:P5, P6

-12 个 I/O 引脚

-唤醒端口: P6

-7 可编程下拉 I/O 引脚

-7 个可编程上拉 I/O 引脚

-7 个可编程开漏 I/O 引脚

-带唤醒功能的外部中断: P60

工作电压范围:

-2.1V~5.5V at 0~70°C(商业)

-2.3V~5.5V at -40~85°C(工业)

工作频率范围(基于 2 个时钟):

-水晶模式:DC~20MHz/2clks @ 5V DC~8MHz/2clks @ 3V DC~4MHz/2clks @ 2.1V

-ERC 模式:

DC~2 MHz/2clks @ 2.1V

-IRC 模式:

|

|

漂移率 |

|||

|

内部 RC 频率 |

温度(-40°C~85°C) |

电压 |

过程 |

总计 |

|

4 兆赫 |

+ 1% |

+ 3% *(2.1~5.5V) |

+ 2% |

+ 6% |

|

16 兆赫 |

+ 1% |

+ 1% *(4.0~5.5V) |

+ 2% |

+ 4% |

|

8 兆赫 |

+ 1% |

+ 2% *(3.0~5.5V) |

+ 2% |

+ 5% |

|

1 兆赫 |

+ 1% |

+ 3% *(2.1~5.5V) |

+ 2% |

+ 6% |

* 工作电压范围

外设 配置

-8 位实时时钟/计数器 (TCC),具有选择性信号源、触发沿和溢出中断

-外部中断输入引脚

由代码选项选择的每个指令周期-2/4个时钟

-掉电(睡眠)模式

-高 EFT 免疫力

四个可用的中断:

-TCC溢出中断

-输入端口状态改变 中断

-外部中断

-低电压检测中断

特殊功能

-可编程自由运行看门狗定时器

-提供开机电压检测器 (1.8~1.9V)

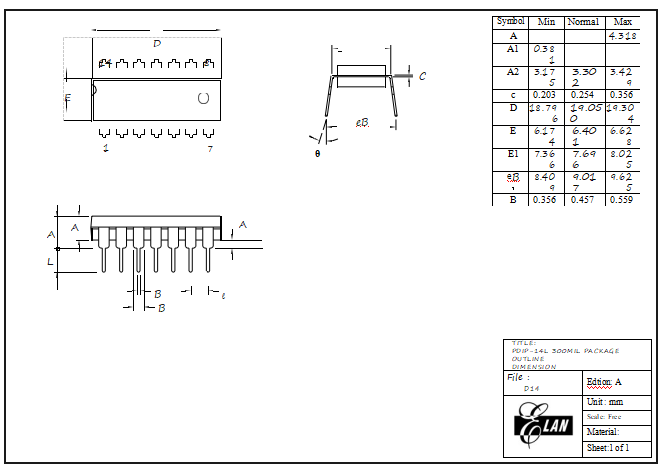

包类型:

-14-piDIP 3亿: EM78P173ND14

-14-pin SOP 150mil : EM78P173NSO14

-10-pin MSOP 118mil : EM78P173NMS10

注意:这些都是不含有害物质的绿色产品

引脚分配

|

(1) 14-Pin DIP/SOP

|

(1) 10-Pin MSOP

|

引脚说明

| 名称 | 功能 | 输入类型 | 输出类型 | 说明 |

| P50~P52 | P50~P52 | ST | CMOS | 具有可编程下拉功能的双向 I/O 引脚。 |

| P53 | P53 | ST | CMOS | 双向 I/O 引脚 |

|

P60//INT |

P60 |

ST |

CMOS |

具有可编程下拉、开漏、上拉和引脚变化唤醒功能的双向 I/O 引脚。 |

| /INT | ST | - | 外部中断引脚 | |

|

P61 |

P61 |

ST |

CMOS |

具有可编程下拉、开漏、上拉和引脚变化唤醒功能的双向 I/O 引脚。 |

|

P62/TCC |

P62 |

ST |

CMOS |

具有可编程下拉、开漏、上拉和引脚变化唤醒功能的双向 I/O 引脚。 |

| TCC | ST | - | 实时时钟/计数器时钟输入 | |

|

P63//重置 |

P63 |

ST |

CMOS |

具有可编程下拉和引脚变化唤醒的双向 I/O 引脚。 (开漏) |

| /重置 | ST | - | 外部上拉复位引脚 | |

|

P64/OSCO/RCOUT |

P64 |

ST |

CMOS |

具有可编程开漏、上拉和引脚变化唤醒功能的双向 I/O 引脚。 |

| OSCO | - | XTAL | 晶体/谐振器的时钟输出 | |

|

RCOUT |

- |

CMOS |

内部RC振荡器的时钟输出外部RC振荡器的时钟输出(open-drain) | |

|

P65/OSCI/ERCin |

P65 |

ST |

CMOS |

具有可编程开漏、上拉和引脚变化唤醒功能的双向 I/O 引脚 |

| OSCI | XTAL | - | 晶体/谐振器的时钟输入 | |

| ERCin | AN | - | 外部 RC 输入引脚 | |

|

P66~P67 |

P66~P67 |

ST |

CMOS |

具有可编程开漏、上拉和引脚变化唤醒功能的双向 I/O 引脚 |

| VDD | VDD | 电源 | - | 电源 |

| VSS | VSS | 电源 | - | 地面 |

图例: ST:施密特触发器输入 CMOS:CMOS 输出 AN:模拟引脚 XTAL:晶体/谐振器的振荡引脚

EM78P173N 功能框图

封装说明

14-引线塑料双列直插式封装 (PDIP) — 300 mil

B-1a EM78P173N 14 引脚 PDIP 封装类型

功能说明

6.1 操作寄存器

6.1.1R0(间接寻址寄存器)

R0 不是物理实现的寄存器。 它用作间接寻址指针。 任何使用 R0 作为指针的指令实际上都会访问 RAM 选择寄存器 (R4) 所指向的数据。

6.1.2R1(定时器时钟/计数器)

由外部信号边沿增加,由TE 位(CONT-4)通过TCC 引脚定义,或由指令周期时钟增加。

与任何其他寄存器一样可写和可读。

通过重置 PAB (CONT-3) 定义。

∎ 如果 PAB 位 (CONT-3) 复位,则预分频器分配给 TCC。

∎ 预分频计数器的内容只有在 TCC 寄存器被写入一个值时才会被清除。

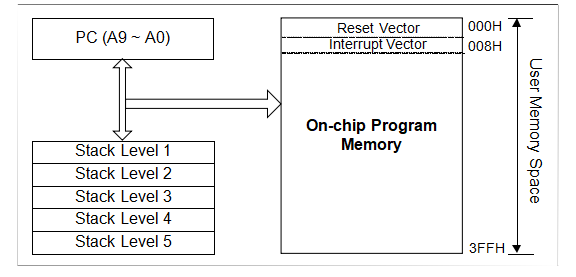

6.1.3R2(程序计数器和堆栈)

∎ 根据设备类型,R2 和硬件堆栈为 10 位宽。 其结构如下图所示。

当ICE300N尝试模拟EM78P173N的堆叠时,当模拟堆叠超过5层时,模拟结果将与EM78P173N不一致。

配置结构生成1024×13 位的片上OTP ROM 地址到相关的编程指令代码。一个程序页长 1024 个字。

R2 在复位状态下设置为全“0”。

“JMP”指令允许直接加载程序计数器的低 10 位。因此,“JMP”允许 PC 转到页面内的任何位置。

“CALL”指令加载PC的低10位,然后PC+1被压入堆栈。因此,子程序入口地址可以位于页面内的任何位置。

"RET" ("RETLk", "RETI") 指令将顶层堆栈的内容加载到程序计数器中。

“ADD R2,A”允许在当前PC上增加一个相对地址,PC的第9位和第10位会逐渐增加。

“MOV R2,A”允许从“A”寄存器加载一个地址到PC的低8位,PC的第9和第10位(A8~A9)保持不变。

任何写入 R2 的指令(“ADD R2,A”除外)(例如,“MOV R2, A”、“BC R2, 6”等)都会导致 PC 的第 9 位及以上位保持不变。

∎ 所有指令都是单指令周期(fclk/2 或 fclk/4),除了会改变 R2 内容的指令。这样的指令将需要多一个指令周期。

质量保证和可靠性

| 测试类别 | 测试条件 | 备注 |

|

可焊性 |

焊料温度 = 245 ±5°C,使用松香型助焊剂保持 5 秒直至塞子 |

– |

|

前提条件 |

步骤 1:TCT,65°C(15 分钟)~150°C(15 分钟),10 个循环 |

SMD IC(如SOP、QFP、SOJ等) |

| 第 2 步:在 125°C 下烘烤,TD(耐力)= 24 小时 | ||

| 第 3 步:在 30°C/60% 下浸泡,TD(耐力)= 192 小时 | ||

| 第 4 步:IR 流 3 个周期

(Pkg 厚度 ³ 2.5mm 或 包装体积 ³ 350 mm3 225 5°C) (Pkg 厚度 & 2.5 毫米或 包装体积 350 mm3 240 5°C) |

||

| 温度循环测试 |

-65°C (15 min) ~ 150°C (15 min), 200 个循环 |

– |

|

压力锅测试 |

TA = 121°C,RH = 100%,压力 = 2 atm,TD(耐力)= 96 小时 |

– |

| 高温/高湿测试 |

TA = 85°C , RH = 85%, TD (耐力) = 168 , 500 小时 |

– |

| 高温储存寿命 |

TA = 150°C,TD(耐力)= 500, 1000 小时 |

– |

| 高温工作寿命 | TA = 125°C,VCC = 最大值。工作电压,TD(耐力)= 168, 500, 1000 hrs |

– |

| 闩锁 | TA = 25°C,VCC = 最大值。工作电压,800mA/40V | – |

|

ESD (HBM) |

TA = 25°C, ³∣± 4KV∣ |

IP_ND,OP_ND,IO_ND IP_NS,OP_NS,IO_NS IP_PD,OP_PD,IO_PD,IP_PS,OP_PS,IO_PS,VDD-VSS(+),VDD_VSS

(-) 模式 |

|

ESD (MM) |

TA = 25°C,³ ∣± 400V∣ |