应广单片机PADAUK开发环境V0.81版本是一个专为PADAUK系列微控制器设计的集成开发环境(IDE),适用于嵌入式系统开发者

PADAUK单片机,作为应广科技(Winbond Electronics)旗下的一款重要产品,确实在电子行业中占据了重要位置,尤其是在那些对成本、能效和可靠性有较高要求的领域。下面是对PADAUK单片机及其开发环境更详细的介绍:

应广科技PADAUK单片机特点

- 高效能与低功耗:PADAUK单片机设计时就考虑到了在保持高性能的同时降低功耗,这对于延长电池寿命、减少能源消耗具有重要意义,特别是在便携式设备和电池供电的应用中。

- 成本效益:相较于其他品牌的同类产品,PADAUK单片机以其合理的价格提供了丰富的功能和较高的性能,使得它们在价格敏感型市场(如消费电子产品)中非常受欢迎。

- 广泛应用:由于上述特点,PADAUK单片机被广泛应用于智能家居(如智能门锁、环境监测)、工业控制(如自动化生产线、电机控制)、汽车电子(如车载系统、传感器接口)等多个领域。

- 灵活性和可扩展性:PADAUK单片机系列提供了多种型号,每种型号都有其特定的功能集和性能参数,从而能够满足不同应用场景的需求。

应广科技PADAUK开发环境

PADAUK的开发环境是一个集成了多种开发工具的软件套件,旨在帮助开发者高效地开发针对PADAUK单片机的应用程序。该环境通常包括以下几个核心组件:

- 编译器:将开发者编写的源代码(通常是C或C++语言)转换为目标单片机可执行的机器代码。PADAUK的编译器经过优化,以确保生成的代码既高效又紧凑。

- 调试器:允许开发者在单片机上运行程序时暂停、单步执行、查看和修改内存和寄存器内容,从而定位和解决程序中的错误。PADAUK的调试器通常与IDE(集成开发环境)紧密集成,提供直观的调试界面。

- 模拟器:在没有实际硬件的情况下,模拟单片机运行程序的工具。这对于快速原型设计和初步测试非常有用。

- 项目管理功能:帮助开发者组织和管理项目文件、设置编译选项、跟踪更改历史等。这些功能有助于提高开发效率并降低出错率。

- 文档和示例代码:提供详细的开发文档和丰富的示例代码,帮助开发者快速上手并理解如何使用PADAUK单片机的各种功能。

总之,PADAUK单片机及其开发环境为开发者提供了一个强大而灵活的平台,用于创建高效、可靠且成本效益高的电子应用程序。

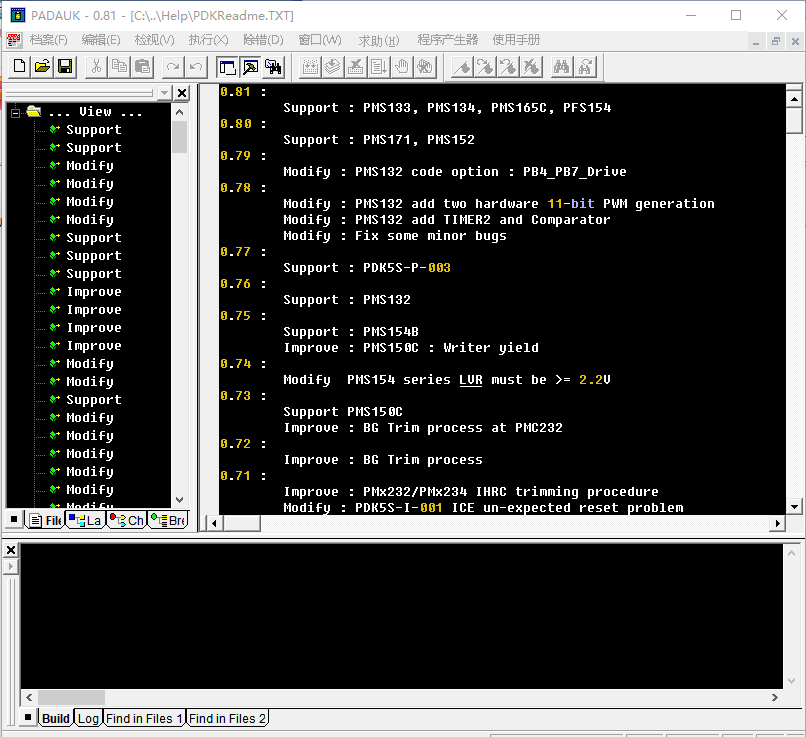

应广单片机PADAUK开发环境V0.81版本是一个专为PADAUK系列微控制器设计的集成开发环境(IDE),适用于嵌入式系统开发者

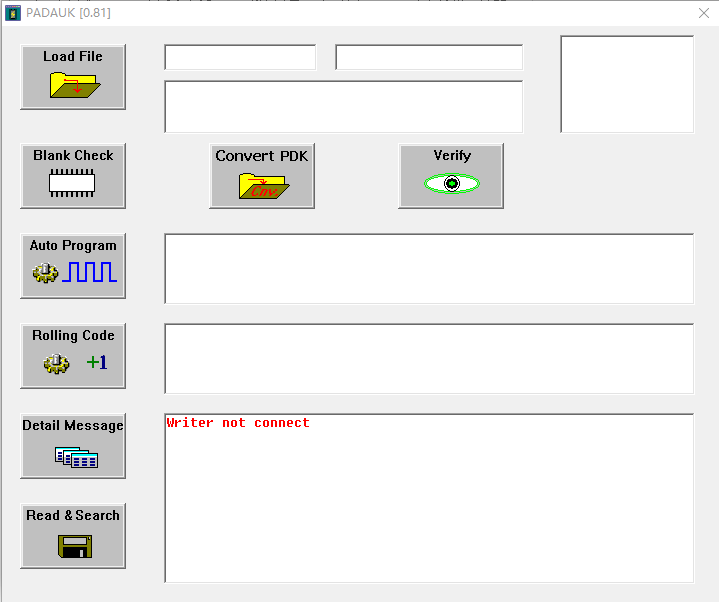

应广单片机烧录器软件界面

MCU_IDE_0.81.exe 文件很可能是这个开发环境的安装程序。运行这个文件,用户可以安装PADAUK V0.81版本的开发环境,然后开始创建和管理他们的项目。IDE中的编译器是至关重要的,因为它将程序员用高级语言编写的源代码转化为单片机可以执行的机器码。这个特定版本的编译器可能具有特定的语法特性、库函数或者优化选项,以适应当时芯片的特性和需求。

在使用这个开发环境时,开发者可以利用其内建的调试工具来定位和修复代码中的错误,这通常包括断点设置、变量查看、步进执行等功能。此外,IDE可能还支持代码编辑器的语法高亮、自动完成等提高开发效率的特性。

应广PADAUK开发环境V0.81版本是一个专门为PADAUK微控制器设计的集成开发环境,包含了一个编译器和其他必要的开发工具。这个版本的备份对于那些需要对老款PADAUK芯片进行维护和开发的工程师来说是宝贵的资源,能够帮助他们继续支持和更新现有项目,而不受官方最新版本变动的影响。

1. FPPA 说明:

FPPA 为 IC 的一个执行核心。依不同系列 IC,可分为多核、双核、单双核、单核。

2. FPPA 指令执行速度:

| PADAUK IC 分类 | FPPA 执行速度 | 代表型号 |

|---|---|---|

| 多 核 | 依 PMODE 指令设定 | PDK8xxx |

| 双 核 | System Clock / 2 | P2xxx |

| 单 核 | System Clock | PMC1xx |

| 单双核 | 由 Code Option 决定单/双核 | PMC2xx |

IHRC (ILRC/EOSC) 通过 CLKMD 缓存器设定,输出 System Clock; System Clock 经由上表的设定,输出 FPPA Clock。 大部份指令只须要一个 FPPA Clock 就可以完成,底下是不为 1T 的指令。

| FPPA 数目 | 2 T 指令 | 2T/1T 指令(当 Skip Next 发生时为 2T) |

|---|---|---|

| 双核以上 | IDXM, PUSHW, POPW, LDTABx | --- |

| 单 核 | GOTO, CALL, IDXM, PCADD, RETx | CEQSN, CNEQSN, T0SN, T1SN, IZSN, DZSN |

3. FPPEN: 双核以上的 IC 皆有一个 FPPEN 缓存器。FPPEN 控制着每一个 FPPA 的执行与停止。 预设为 FPPA0 是执行,其他 FPPA 为停止。 此一缓存器的设定不影响每个 FPPA 执行的速度。

缓存器介绍

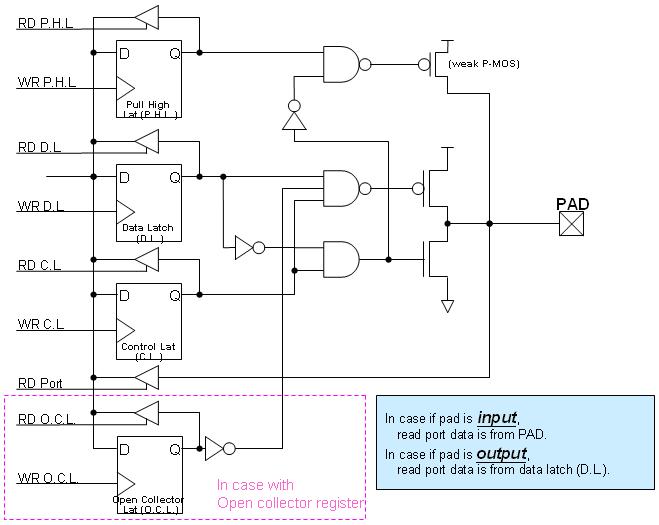

1). 一般 IO 架构图:

一般 IO 输出入表:(以 PA 为例)

| PAC.x | PA.x | PAPH.x | |

|---|---|---|---|

| Output High | 1 | 1 | X |

| Output Low | 1 | 0 | X |

| Input + Pull High | 0 | X | 1 |

| Input | 0 | X | 0 |

PAC.x PA.x PAPH.x Output High 1 1 X Output Low 1 0 X Input + Pull High 0 X 1 Input 0 X 0

Pull High 在 Output Low 时,是自动被关闭的。

至于 Output High 时,有无 Pull High,影响不大。

(3). 简易 IO 语法,请参考如下范例:

$ PA.0 Out, High; // PA.0 输出 High

$ PA.1 Out, Low, In; // PA.1 输出 Low 后,再切为 Input

$ PA.2 In, Pull; // PA.2 输入 并 Pull High

$ PA.3 NoPull; // PA.3 的 Pull High 关掉

【一般注意事项】

(1). 未使用的 IO 脚:

如果 IO 脚没有使用,请将它设为固定准位,如:

Output High 或 Output Low 或 Input + Pull High 或 模拟输入脚。

如 IO 脚只能当作单纯 Input 脚 (如有些型号的 PA5),请将它接到 VDD 或 GND。

(2). Pull High 的注意事项:

一般在 5V 时,Pull High 电阻约在 80K 附近,

不同的 IC、电压、温度,都会使 Pull High 电阻不同,

如果你想利用它来做一般按键的 Pull High,是足够的,

但如果作通讯用的 Pull High (如 I2C 接口),却是不行的。

很多系列的 PAPH、PBPH 是 Write Only,所以你不可以对它们作

SET0、SET1、SWAPC、TOG、XOR 指令。

因为以上指令的运作原理,是先读回 IO 的值,然后作

AND(SET0) / OR(SET1) / MOV(SWAPC) / XOR(TOG) 运算,

等设定相对应的 BIT 后,再整个 Byte 写回 IO。

那既然 PAPH、PBPH 是 Write Only,所以,就无法读回 IO 的值,也就无法使用了。

(3). Open Drain 的注意事项:

并不是所有系列都支持 Open Drain Mode,它可以被 I/O 的三态取代。

若 IO 口设为 Open Drain,当输出为 Open 时,

从 IO 口读回的值,将是 1,而不是 Input 的值。

如果你想作 I2C 的传输,建议你可从 Code Generate 中得到 I2C 的 Sample Code。

不过在 Sample Code 中,只用输出/输入切换完成 I2C 的传输,而不使用 Open Drain。

(4). 过电压的输入保护:

如果你的 IO 输入口,有高于 VCC 的电压输入,而又无法避免时,

请在 IO 口串连上一个电阻。

建议的电阻值为: 电压差(Volt.) × 100KΩ。

以下为例,VCC=5V,外部有一个 15V 的电源讯号到 IO 口,所以需接保护电阻:

电压差 (15V - 5V = 10V) × 100KΩ = 1MΩ 电阻。

(5). IO 的输入阻抗有多大 ?

由于一般三用电表只能量测到 20 M 的电阻,所以 IO 的输入阻抗,大到无法量测。

【共享其他功能】

(1). IO 与 Reset 共享时的注意事项:

在 IO 口中的 PA.5,并不存在 Pull High 的功能,也无法 Drive High。

当 PA.5 为输入脚时,如果没有使用,建议接到 VDD 或 GND。

只有 PAC.5 = 0 (Input) 时,才可以从 PA.5 读回输入脚,

当 PAC.5 = 1 (Output) 时,是无法读回输入脚。

我们可以利用切换 CLKMD.0,使 PA.5 成为 IC 的外界重置讯号源。

SET0 CLKMD.0 // 设定 PA5 是输入脚,这是系统默认值。

SET1 CLKMD.0 // 设定 PA5 是外界的重置讯号源。

附注: (1): 至于其它的 IO 口,都有输出入切换与选择 Pull High 的功能。

(2): 有些系列的 IC (如 P234/..),增加了 PA5 Output Low 的功能。

(2). IO 与 External Crystal 共享时的注意事项:

当硬件的 EOSCR.7 设为 1 时,IO 口的 PA.6 / PA.7 会用来起振 Crystal。

为了兼容性起见,使用 Crystal 时,需设定 PA.6 / PA.7 为 Input + No Pull High。

请参考范例 【PDK82系列 & Crystal】。

【PDK22系列 & Crystal】。

【P234 / P201A 系列 & Crystal】。

在使用 ICE 时,请注意版子上 SW3 的切换。

在使用 PA.6 / PA.7 作一般 I/O 口时,请将版子上的 SW3 切为 ON。

在使用 Crystal 时,请将版子上的 SW3 切为 Off,以隔离外部讯号的干扰。

(3). IO 与 ADC 共享时的注意事项:

当你将 IO 用于 ADC 的转换时,请记得要设为 输入状态 与 致能模拟输入脚。

( ADCDI / PBDIDR / … 的功能主要在切断输入端的耗电,使 ADC 的准确度提升)。

范例: 将 PB 的 7~4 设成 AD 输入端,其余为输出端。

PBC = 0x0F; // PB 的 7~4 设为输入状态。

ADCDI = 0xF0; // (a) 切断 PB 的 7~4 的输入端的耗电。

或

PBDIDR = 0xF0; // (b) 切断 PB 的 7~4 的输入端的耗电。

(附注: 由于不同系列 IC,造成同一功能有(a)(b)不同名称,十分抱歉。)

【SET0/1 IO.bit 的注意事项】

当对 IO 口作 SET0/1、SWAPC、TOG、XOR 指令,运作的原理,是先读回 IO 口的值,

然后作 AND(SET0) / OR(SET1) / MOV(SWAPC) / XOR(TOG) 运算,等设定相对应的 BIT 后,

再整个 Byte 写回 IO 口。

以下为范例:

PA.0 = 0; // (*1) PA.0 的 Data = 0;

…

PAC.0 = 0; // (*2) PA.0 -> Input Mode

…

… // (*3) PA.0 的外界讯号为 High or Low ??

…

PA.1 = 0; // (*4) 也影响了 PA.0 的 Data

…

PAC.0 = 1; // (*5) PA.0 -> Output High or Low ??

(*1) 一开始虽然设定 PA.0 的 Data = 0,

(*2) 但只要中途 PAC.0 改设成 Input Mode,

(*3) 而且 PA.0 的 Pin 因外界讯号影响,而成为 High,

(*4) 只要 PA.1 = 0 的指令被执行时,

PA 先被读回,数值为 0Bxxxx_xxx1,

作 AND Bit 1 运算,动作为 ( &= 0B1111_1101 ),

最后写回 PA (Data Register) 为 0Bxxxx_xx01,

所以,PA.1 的 Data = 0,PA.0 的 Data = 1,

(*5) 当 PAC.0 = 1 又设回 Output Mode 时,

PA.0 将意外成为输出 High (Data = 1)。

这种现象在大部份的 MCU 皆存在,一般要将 IO 口从 Input 改为 Output High / Low,

都是先设定 PA (Data Register),再改变 PAC (Control Register)。

PAC.0 = 0; // PA.0 -> Input Mode

…

PA.0 = 0; PAC.0 = 1; // PA.0 -> Output Low

不过在 FPPA 中,须注意有以下例外。如下例,FPPA0 使用 PA0,FPPA1 使用 PA1,

假设 PA0 为 Input Mode,且因外界讯号影响而为 High。

而此时,你想将 PA.0 设为 Output Low。不过 FPPA1 正好也在设定 PA1。

时序 FPPA0 FPPA1

1 SET0 PA.0

2 TOG PA.1

3 SET1 PAC.0

FPPA0 原以为在 时序 1 时将 PA.0 的 Data 设为 0,

结果 时序 2 时,FPPA1 的 TOG 指令,让 PA.0 的 Data 又更新为 1,

结果 时序 3 时,PA.0 输出为 High 了。

如果改成如下程序:

时序 FPPA0 FPPA1

1 TOG PA.1

2 SET1 PAC.0

3 …

4 SET0 PA.0

此时 PA.0 正确的输出为 Low;但在 时序 2 时,却不知 PA.0 的 Data 值为何,

所以在时序 2 ~ 4 时,可能输出一个短暂的 High Pulse。

也有人改写成如下程序:

时序 FPPA0 FPPA1

1 …

2 SET0 PA.0

3 TOG PA.1

4 SET1 PAC.0

5 …

6 SET0 PA.0

FPPA0 在 时序 2 时,初始了 PA.0 的 Data,

所以大部份的机率,PA.0 都会正确的从 Input 转成 Output Low;

但是如果在 时序 3 时,FPPA1 正好执行 SET0/1、TOG… 的指令,

还是有可能使 PA.0 在 时序 4 ~ 6 时,输出一个短暂的 High Pulse。

所以,如果你有可能多个 FPPA 共享一个 IO 口,并且你要作 Input/Output 切换,记住:

先设定 Control Register,再设定 Data Register。

在实际应用的例子上,I2C 的 Data Pin,是属于 In/Out 切换的模式,可不要忘记这规则。

以下为实际范例,假设你有一个 FPPA 须要对 PA 的两个 IO 脚要作 In / Out 切换:

BIT pin_IO_S0 : PA.0;

BIT pin_IO_S1 : PA.1;

(a) 如果其它 FPPA 不会对 PA 有 SET0/1、SWAPC、TOG、XOR 等指令,程序可如下撰写:

$ pin_IO_S0 IN; // 设定为 Input

$ pin_IO_S1 IN;

…

$ pin_IO_S0 LOW, OUT; // 设定为 Output Low

$ pin_IO_S1 HIGH, OUT; // 设定为 Output High

(b) 如果其它 FPPA 也会对 PA 有 SET0/1、SWAPC、TOG、XOR 等指令,程序可如下撰写:

$ pin_IO_S0 IN; // 设定为 Input

$ pin_IO_S1 IN;

…

$ pin_IO_S0 LOW, OUT, LOW; // 设定为 Output Low

$ pin_IO_S1 HIGH, OUT, HIGH;// 设定为 Output High

总结来说,最建议的写法,是如上的红色范例最好。

【IO共享的注意事项】

当不同的 FPPA,共享同一个 IO 口时,总会遇到许多困扰。

除了共享单一 Pin,可用 SET0/1 IO.bit 解决外,

对于同一个 IO 口的多个 Pin 要同时被设定,就得用设立临界区的技巧来解决。

BIT Enable : GDIO.0;

void Get_Enable (void)

{ // 要更改 IO 前,须先进入循环,且等到 CF == 1 才可离开。

CF = 0;

do

{ // SWAPC => 在一个指令周期内,作完

swapc Enable; // CF = Enable,Enable = 0。

} while (! CF); // if (CF == 1) then can return

}

void FPPA0 (void)

{

// … // 程序一开始,

Enable = 1; // 须先初始 致能旗标 = 1;

// …

{

Get_Enable (); // 进入临界区后,

PA = xxx; // 方可更改 IO,

… // 离开临界区前,

Enable = 1; // 归还 致能旗标。

}

// …

}

void FPPA1 (void)

{

// …

{

Get_Enable (); // 进入临界区时,

PA = xxx; // 才可更改 IO,

… // 离开临界区后,

Enable = 1; // 归还 致能旗标。

}

// …

}

这个方法的优点是进入临界区后,IO 口可随意更改,

缺点则是取得进入临界区的时间不固定。

在有些系列的 IC,新增加了指令 XOR A, IO / XOR IO, A,

也很适用于 IO 共享。