PGS134应广单片机系统特性

1. 4KW 程序储存器

2. 512 Bytes EEPROM

3. 256 Bytes 数据存储器(128*16)

4. 一个16位定时器

5. 两个8位定时器(可做为PWM产生器)

6. 三个11位PWM生成器(PWMG0,PWMG1,PWMG2)

7. 提供一个比较器

8. Band-gap 电路提供1.2V参考电压

9. 最高可提供14通道的12位ADC,其中一个来自于内部band-gap参考电压或者0.25*VDD

10. ADC 参考高电压:外部输入, 内部VDD, Band-gap 1.2V, 1.6V, 2.0V, 2.4V, 3.0V, 4.0V

11. 支持乘法指令 (1T 8x8)

12. 22 个IO 引脚带有上拉及下拉电阻选项

13. 提供两种不同的IO驱动能力以满足不同的应用需求

(1) PB4,PB7驱动/灌电流= 30mA/35mA (Strong) and 13mA/17mA (Normal)

(2) 其他 IO 驱动/灌电流 = 11mA/(13 or 20) mA

14. 每个IO 引脚都可设定唤醒功能

15. 内建 1/2 VDD LCD 偏置电压生成器,可支持最大 4x17 点阵的 LCD屏幕

16. 时钟源:IHRC,ILRC及EOSC(XTAL)

17. 对所有带唤醒功能的IO,都支持两种可选择地唤醒速度:正常唤醒与快速唤醒

18. 八段LVR 复位电压设定: 4.0V, 3.5V, 3.0V, 2.7V, 2.5V, 2.2V, 2.0V, 1.8V

19. 两组依Code Option 选择的外部中断引脚

CPU 特性

1. 8bit 高性能RISC CPU

2. 提供98 个有效指令

3. 1T(单周期)指令

4. 可程序设定的堆栈指针和堆栈深度

5. 数据存取支持直接和间接寻址模式,

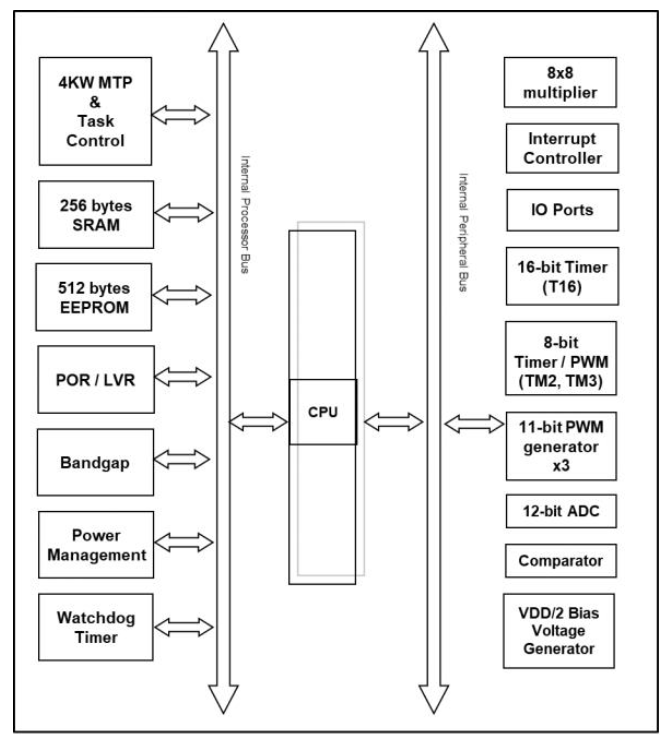

系统概述和方框图

PGS134 系列是一款带 12bit ADC,以 MTP 为程序基础的 CMOS 8-bit 微处理器。它运用 RISC 的架构并且

所有的指令架构的执行周期都是一个指令周期,只有少部分指令需要两个指令周期。

内部最多达 4KW MTP 程序存储器、512 字节 EEPROM 以及 256 字节数据存储器,还有多达 14 通道 12 位

分辨率的 ADC,其中一个通道是带有多个内部参考电压可供选择。PGS134 同时提供 6 个硬件计数器:一个 16

位的硬件计数器,两个 8 位 PWM 计数器,和三个 11 位 PWM 计数器。另外,PGS134 还提供一个硬件比较器和

驱动 LCD 的 1/2 VDD 偏置电压。

引脚功能说明

直流交流电气特性

| 符号 | 描述 | 最小值 | 典型值 | 最大值 | 单位 | 条件(Ta=25℃) |

| VDD | 工作电压 | 2.2* | 5.0 | 5.5 | V | #受限于LVR公差 |

| LVR% | 低电压复位公差 | 5 | 5 | % | ||

| fsys | 系统时钟(CLK)*= HRC/2 HRC/4 IHRC/8 ILRC |

0 0 0 |

82K | 8M 4M 2M |

Hz | Voo ≥3.5V Voo≥2.5V Voo ≥2.2V Vop=5.0V |

| Peycle | EEPROM烧录次数 | 100K | Cycle | |||

| Pread | EEPROM读取电压 | 2.2= | VDD | V | VDD电压 | |

| Ppgm | EEPROM擦除/写入电压 | 2.2= | VDo | V | #Vpo电压 | |

| VPOR | 上电复位电压 | 2.0* | ±受限于LVR公差 | |||

| loP | 工作电流 | 0.6 80 |

mA uA |

fsrs=IHRC/16=1MIPS@5.0V fsvs=ILRC=82KHz@3.3V |

||

| IPD | 掉电模式下电流 (使用stopsys命令) |

0.9 0.5 |

uA uA |

fsrs=0Hz,Vpp=5.0V fsys=0Hz,Voo =3.3V |

||

| lPs | 省电模式下电流 (使用stopexe命令) |

4.0 | uA | Vpo=5.0V;fsys=ILRC 只启用ILRC模块 |

||

| VL | 输入低电压 | 0 | 0.2 Vp | V | ||

| VIH | 输入高电压 | 0.7 VoD | VDD | V | ||

| loL | O输出灌电流(可通过Code Option"PB4_PB7_Drive"切换PB4/PB7电流 | |||||

| PB4,PB7 (Normal PB4,PB7 (Strong PA0-4,PB2,PB5-6 PA5-7,PB0-1,PB3,PC0-5 |

24 40 25 15 |

mA | Voo=5.0V,Vou=0.5V | |||

| loH | O输出驱动电流 | |||||

| PB4,PB7 (Normal) PB4,PB7 (Strong Other lOs |

17 32 14 |

mA | Voo=5.0V,Voh=4.5V | |||

| ViN | 输入电压 | 0.3 | Vop +0.3 | V | ||

| INJ(PIN | 引脚输入电流 | 1 | mA | VDD+0.3兰VN兰-0.3 | ||

| RPH | 上拉电阻 | 62 | KΩ | Vpp =5.0V | ||

| VBG | Bandgap参考电压 | 1.145* | 1.20* | 1.255* | V | Vpp =2.2V~5.5V -40℃ |

| fiHRC | 校准后IHRC频率 | 15.76* | 16* | 16.24* | MHz | 25°C,Voo =2.2V~5.5V |

| 15.20* | 16* | 16.80* | Voo =2.2V~5.5V 40℃ |

|||

| tiNT | 中断脉冲宽度 | 30 | ns | Voo=5.0V | ||

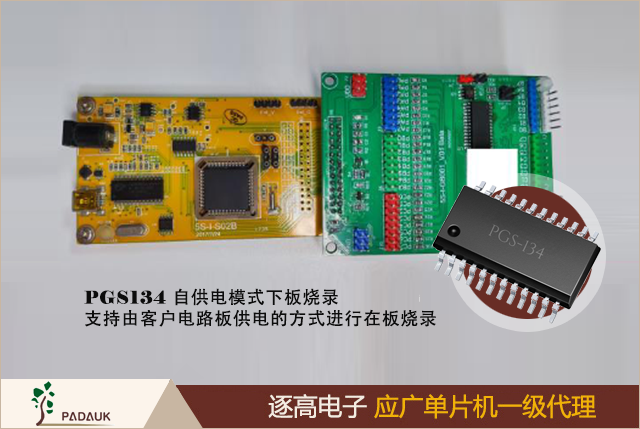

烧录方法

请使用 5S-P-003(B)进行烧录。3S-P-002 以及之前的烧录器皆不支持 PGS134 的烧录。

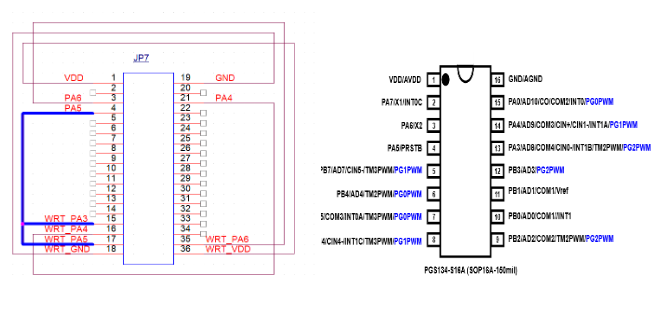

l PGS134 的烧录脚为 PA4,PA5,PA6,VDD,GND 这 5 只引脚。

l 当合封(MCP)或在板烧录时,关于电压与电流的特别注意事项:

(1) PA5 (VPP) 可能高于 5.5V。

(2) VDD 可能高于 5.5V,且其最大电流可能到达 20mA。

(3) 其他烧录引脚(GND 除外)与 VDD 相同。

(4) 当用户使用 MCP 或在板烧录时,用户需要确认,外围电路或元件不会被上述电压所破坏或限制上述电

压的产生。

重要提示:

(1) 如在 handler 上对 IC 进行烧录,请务必按照 APN004 及 APN011 的指示进行。

(2) 为对抗烧录时的杂讯干扰,请于烧录时在分选机连接 IC 连接器一端的 VDD 和 GND 之间连接 0.01uF

电容。但切忌连接标值 0.01uF 以上的电容,以免影响普通烧录模式的运行。

请用户依据实际情况选择下述烧录模式。

普通烧录模式

Jumper 连接:可依照烧录器软件上的说明,连接 jumper 即可。请参考烧录器“5S-P-003”的用户手册,

了解当使用 5S-P-003(B) 烧录时使用的 JP7 跳线方式。

注意:除了 ICVPP(PA5)需要通过 JP7 跳线与 IC 的 PA5 短接外, ICVPP2(PA3)也必须与 IC 的 PA5 短接。

例如,PGS134-SOP16A 在烧录器上的 JP7 跳线信号连接图,如下所示:

在板烧录模式

所谓在板烧录,是指 IC 及其他周边电路及组件,皆已经焊接到 PCB 上,并对 IC 进行烧录的情况。在板

烧录需要使用 5S-P-003 上五根引线:ICPCK(PA4)、ICPDA(PA6)、VDD、GND、ICVPP(PA5) 。

图 23 中的‘☆’可代表电容或电阻。用于隔离烧录引线和其他电路。电阻应≧10KΩ,电容应≦220pF。

注意:

l 一般来说,在板烧录应使用限压烧录模式。请参考在限压烧录模式的详细说明。

l PCB 上的 VDD 与 GND 之间不可连接有 5.0V 或以下的稳压二极管或其他钳制 5.0V 产生的电路或

元件。

l PCB 上的 VDD 与 GND 之间不可连接有标值 500uF 或以上的电容器。

l 一般来说,用于烧录讯号的 PA4,PA5 及 PA6 引脚,不能作为强输出脚。

自供电模式下的在板烧录

PGS134 同样支持由客户电路板供电的方式进行在板烧录。想要使用此功能需在烧录文件设定”On-board

Program w/ Self-Power”, 可在烧录器软件 To Package 的选单中设置。或是在原代码中以命令的方式加入封装

参数设置中,详细操作可参考烧录器使用说明书。

烧录器将在烧录前侦测客户电路板上的 VDD 电压。所以请保证电路板上的 VDD 电压高于 2.5V,应用板上

的 VDD 电压若低于 2.5V 烧录器将会显示错误”Find a diff. IC.”。 其余与烧录器供电的在板烧录模式相同。

Converter PDK to Package:

勾选自供电 ISP 选项时,若 CodeOption PAC.5 设为 Enable 时,当 PA5 输出低,烧录可能会损坏 IC。

因此 PA5 设置为 0utput 时,可支持板上自供电的 ISP Mode,但不建议使用。

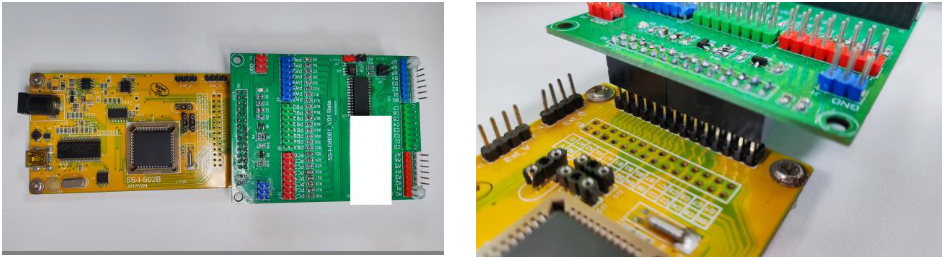

使用 ICE

仿真 PGS134 请使用 5S-I-S01/2(B)外挂仿真板 5S-I-GB001,参考如下图片:

仿真时请注意以下事项:

(1) 关于仿真时序

l 仿真时,尤其是仿真 EEPROM 和 PxPL 相关功能时,5S-I-S01/2(B)会和仿真板 5S-I-GB001 进行通信,

所以仿真时许会略慢于实际 IC,主要影响以下寄存器配置

EERL/EERMC/STEER/LDEER/MISC2/INTRQ/INTRQ2/PAPL/PBPL/PCPL/LPWMGxC/LPWMGxDTH

/LPWMGxDTL /LPWMGCLK/LPWMBCUBH/LPWMCUBL 等

(2) 关于仿真电压

l 仿真时,受仿真板工作电压影响,建议仿真电压≥2.5V

(3) 其他注意事项

l 5S-I-S01/2(B)仿真时,不支持指令 NMOV/SWAP/NADD/COMP 的 RAM 运算。

l 5S-I-S01/2(B)仿真时,不支持 SYSCLK=ILRC/16。

l 5S-I-S01/2(B)仿真时,不支持 misc.4 动态设定(只能固定为 0 或 1)。

l 5S-I-S01/2(B)仿真时,不支持 Tm2.gpcrs/Tm3.gpcrs 功能。